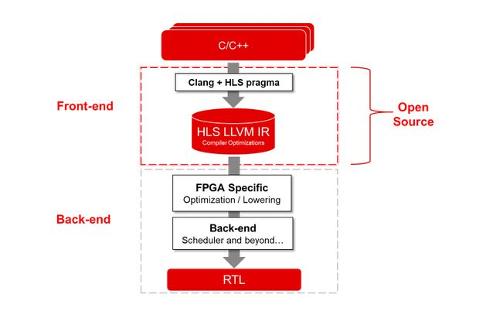

Компания Xilinx, выпускающая интегральные микросхемы программируемой логики, открыла исходный код Vitis HLS — набора инструментов, который позволяет синтезировать высокоуровневое описание логической структуры FPGA из кода на Си/Си++ (в том числе с использованием OpenCL).

По словам представителя компании, публикация исходного кода интерфейса Vitis HLS открывает новые возможности для исследователей, разработчиков и энтузиастов компиляторов в использовании и модификации Vitis HLS в соответствии с конкретными потребностями своих приложений.

Исходный код опубликован на условиях лицензии Apache 2.0 и доступен в репозитории на GitHub.

>>> Подробности