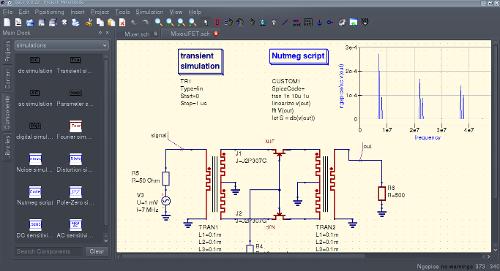

Сегодня, 19 января вышел очередной релиз Qucs-S-0.0.22. Qucs-S является форком проекта Qucs и в отличие от оригинала позволяет использовать не только встроенный движок моделирования, но и внешние Ngspice и XYCE. Это позволяет использовать готовые SPICE-модели электронных компонентов минуя слои совместимости и достичь лучшей скорости и стабильности симулятора. Проект написан на C++ с использованием набора библиотек Qt4.

Список изменений:

- Добавлен компонент SPICEINIT, который позволяет задавать дополнительные настройки для Ngspice;

- Исправлены баги;

Подробности и ссылки на пакеты для Debian, Ubuntu и CentOS есть на странице релиза.